# Design and Performance of Monolithic GaAs Direct-Coupled Preamplifiers and Main Amplifiers

YUHKI IMAI, NAOKI KATO, KUNIKI OHWADA, AND TAKAYUKI SUGETA, MEMBER, IEEE

**Abstract** — The design and performance of a GaAs direct-coupled preamplifier and main amplifier is described. The amplifiers are fabricated by the self-aligned implantation for  $n^+$ -layer technology (SAINT) process. The developed preamplifiers have 13-dB gain, 3-GHz bandwidth, and 4.8-dB noise figure for the one-stage amplifier, and 22-dB gain, 2.7-GHz bandwidth, and 5.6-dB noise figure for the two-stage amplifier. The developed four-stage main amplifier has 36-dB gain and 1.5-GHz bandwidth with a power consumption of 710 mW. These amplifiers are promising candidates for application to high-speed data communication systems.

## I. INTRODUCTION

OVER THE LAST decade, GaAs FET's have established a solid basis in microwave systems. Moreover, recent advances in GaAs IC technology have made it possible to develop large-scale integration of GaAs FET circuits [1].

Due to their small integration scale, GaAs analog IC's are the nearest candidates for practical application among these IC's. In the analog IC's, monolithic broad-band amplifiers are needed because of their wide applications such as mobile, satellite, and high-speed data communication systems. Therefore, various kinds of amplifiers have been studied [2]–[4]. Among these amplifiers, the direct-coupled amplifiers first reported by D. P. Hornbuckle *et al.* [3], which made use of only FET's, diodes, and resistors, have the advantage of broad bandwidth from dc frequency, small chip sizes, and easy integration with the digital circuits.

For high-speed data communication systems, a low-noise, low-VSWR, and high-gain amplifier is required. Previously reported high-gain direct-coupled amplifiers had multistage constructions with their gain ranging from 26 dB to 42 dB [5], [6]. However, these amplifiers are not necessarily adequate for the above purpose because they were designed for general purpose use. For example, because they consisted of common-gate FET's in the input stages, their noise figure was not enough low (about 9 dB with a 248- $\mu$ m gate-width FET). Moreover, the bandwidth degradation between the stages, which is important for a multistage amplifier, was not discussed.

In this paper, the circuit configurations which are suitable for a low-noise and low-VSWR preamplifier and a high-gain main amplifier are presented, followed by the design considerations including noise figure, input VSWR, and multistage connection. For a preamplifier, a common-source configuration with a resistive feedback from a source-follower stage is newly presented. The amplifiers are fabricated by the self-aligned implantation for  $n^+$ -layer technology (SAINT) process [7]. The developed preamplifiers have 13-dB gain, 3-GHz bandwidth, and 4.8-dB noise figure for a one-stage amplifier, and 22-dB gain, 2.7-GHz bandwidth, and 5.6-dB noise figure for two-stage amplifier. The developed four-stage main amplifier has 36-dB gain and 1.5-GHz bandwidth with a power consumption of 710 mW. These amplifiers are promising candidates for applications to high-speed data communications systems.

## II. FET MODEL FOR THE CIRCUIT DESIGN

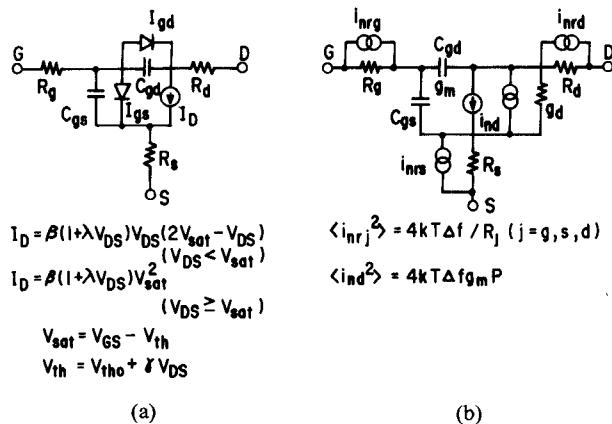

An equivalent circuit and drain current equations used for the circuit design are shown in Fig. 1(a). Drain current  $I_D$  was described in a modified SPICE form [8]. FET parameters used for the circuit design are listed in Table I. The parameters of  $\beta$ ,  $\gamma$ , and  $\lambda$  were determined by fitting the drain  $I$ – $V$  characteristics. Gate-to-source capacitance  $C_{gs}$  and gate-to-drain capacitance  $C_{gd}$  were derived from the change of the charges in the depletion layer under the FET gate [8]. Source resistance  $R_s$  and drain resistance  $R_d$  were estimated by the gate-to-source and gate-to-drain diode characteristics. Gate resistance  $R_g$  was calculated from the gate dimensions.

An equivalent circuit for noise analysis is shown in Fig. 1(b). Noise sources  $\langle i_{nj}^2 \rangle$  ( $j = g$ ,  $s$ , and  $d$ ) and  $\langle i_{nd}^2 \rangle$  represent the thermal noise of  $R_g$ ,  $R_s$ ,  $R_d$ , and drain current noise, respectively. The factor  $P$  for the drain current noise form depended on an FET structure. Therefore, in the noise calculations, it was necessary to vary  $P$  for fitting experimental results. Gate-induced noise was neglected in the present work because it was small in the frequencies below the cutoff frequency.

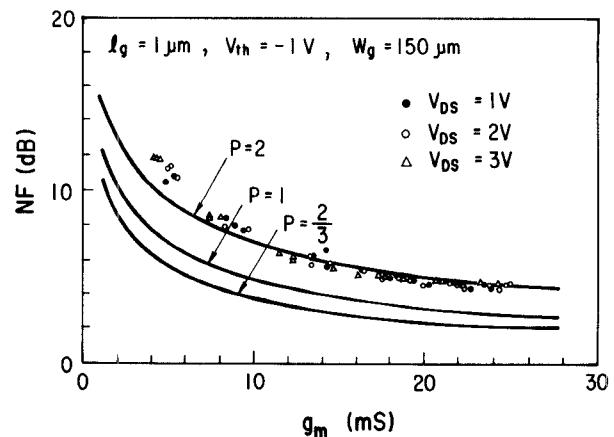

Noise-figure (NF) dependencies on transconductance  $g_m$  were calculated for comparison with the experimental values. The value of factor  $P$  was assumed to be either 2/3, 1, or 2. The noise figure of an FET with a threshold voltage of  $-1$  V and a gate dimension of  $1 \mu\text{m} \times 150 \mu\text{m}$  was

Manuscript received November 27, 1984; revised March 18, 1985.

The authors are with the Atsugi Electrical Communication Laboratory, Nippon Telegraph Telephone Public Corporation, 1839 Ono, Atsugi, Kanagawa, 243-01, Japan.

(a)

(b)

Fig. 1. FET models used for the circuit design. (a) FET model. A drain current  $I_D$  is described by the modified SPICE form with the fitting parameters  $\beta$ ,  $\gamma$ , and  $\lambda$ . (b) FET noise model.  $\langle i_{nrg}^2 \rangle$  and  $\langle i_{nrd}^2 \rangle$  represent thermal noise sources of  $R_g$ ,  $R_s$ , and  $R_d$ , and drain current noise source, respectively.  $P$  is the fitting parameter for the drain current noise.

TABLE I

FET PARAMETERS USED FOR THE CIRCUIT DESIGN

| NAME                                   | SYMBOL    | TYPICAL VALUE              | CONDITION                                |

|----------------------------------------|-----------|----------------------------|------------------------------------------|

| Transconductance parameter             | $\beta$   | 0.06 4A/V <sup>2</sup> /mm | —                                        |

| Channel thickness modulation parameter | $\gamma$  | 0.05                       | —                                        |

| Channel length modulation parameter    | $\lambda$ | 0                          | —                                        |

| Threshold voltage                      | $V_{th}$  | -1.0V                      | $V_{DS} = 2V$                            |

| Gate length                            | $l_g$     | 1.0 $\mu m$                | —                                        |

| Transconductance                       | $g_m$     | 110 mS/mm                  | $V_{DS} = 2V$<br>$V_{GS} = 0V$           |

| Drain conductance                      | $g_d$     | 7 mS/mm                    | $V_{DS} = 2V$<br>$V_{GS} = 0V$           |

| Source resistance                      | $R_s$     | 0.5 $\Omega \cdot mm$      | —                                        |

| Drain resistance                       | $R_d$     | 0.5 $\Omega \cdot mm$      | —                                        |

| Gate resistance                        | $R_g$     | 0.6 $\Omega$               | $W_g = 100 \mu m$<br>$W_{gf} = 50 \mu m$ |

| Gate-to-source capacitance             | $C_{gs}$  | 1.1 pF/mm                  | $V_{DS} = 2V$<br>$V_{GS} = 0V$           |

| Gate-to-drain capacitance              | $C_{gd}$  | 0.1 pF/mm                  | $V_{DS} = 2V$<br>$V_{GS} = 0V$           |

measured at 1 GHz for a 50- $\Omega$  signal-source impedance. The calculated values and measured ones are shown in Fig. 2. The experimental results are located around the calculated curve whose  $P$  was 2. Therefore, it was found possible to design the noise figure of the amplifiers using the appropriate value of  $P$ .

### III. CIRCUIT DESIGNS

All designs were based on computer simulations, with either ASTAP or SPICE, using the FET models mentioned above. In noise calculations,  $P$  was ranged from 2/3 to 2 to obtain general results.

#### A. A Preamplifier

Low noise and low VSWR, as well as broad bandwidth, were required for the preamplifier. From this point of view,

Fig. 2. Noise figure (NF) dependencies on transconductance  $g_m$ . ●○△: Experimental results. —: Calculated results. Noise figure was evaluated at 1 GHz for 50- $\Omega$  signal source impedance.

TABLE II

LOW-VSWR DIRECT-COUPLED AMPLIFIERS WITH SIMPLIFIED FORMS OF THEIR NOISE FIGURE NF AND INPUT IMPEDANCE  $Z_{in}$

|          | (a)                                                                                       | (b)                        | (c)                                             |

|----------|-------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------|

| Circuit  |                                                                                           |                            |                                                 |

| NF       | $1 + \frac{R_{ss}}{R_I} + \frac{P}{g_m R_{ss}} \left( \frac{R_{ss} + R_I}{R_I} \right)^2$ | $1 + \frac{P}{g_m R_{ss}}$ | $1 + \frac{R_{ss}}{R_f} + \frac{P}{g_m R_{ss}}$ |

| $Z_{in}$ | $R_I$                                                                                     | $\frac{1}{g_m}$            | $\frac{1 + g'_m R_f}{g'_m (g_m R_I + 1)}$       |

$R_{ss}$ : Signal-source impedance.  $g_m$ : Transconductance of input FET.  $g'_m$ : Transconductance of source-follower FET.

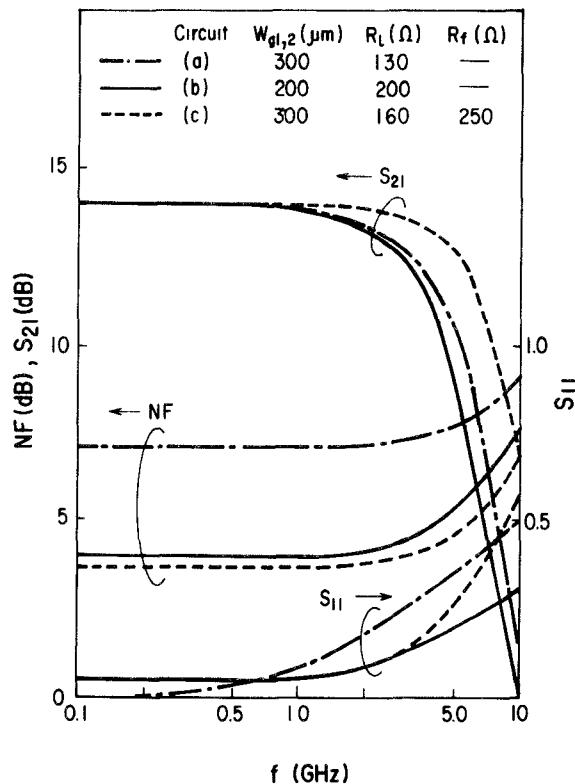

optimum preamplifier circuit construction was studied. Table II shows three kinds of direct-coupled and low-VSWR amplifiers with the simplified forms of their noise figure and input impedance. Circuit (a) consists of a common-source FET with a matching resistor  $R_I$  parallel to the input port. Circuit (b) consists of a common-gate FET. Circuit (c) consists of a common-source FET with a feedback resistor  $R_f$ . The noise figure of circuit (a) was degraded 3–6 dB by the matching resistor. For circuits (b) and (c), noise figures were improved by increasing the gate width of the input FET's. For circuit (b), this improvement was limited because the gate width must be determined to satisfy an input matching condition. For circuit (c), the gate width was increased without any effect on the input matching condition. Therefore, the noise figure of circuit (c) was improved more than that of circuit (b) by choosing the appropriate values of the gate width and the feedback resistor. The results calculated by the computer are shown

Fig. 3. Simulated frequency dependencies of transducer gain  $S_{21}$ , input reflection coefficient  $S_{11}$ , and noise figure NF for circuits (a), (b), and (c).

in Fig. 3. In this figure, the frequency dependencies of transducer gain  $S_{21}$ , input reflection coefficient  $S_{11}$ , and noise figure NF, calculated with  $P$  of 1, were compared under the constant- $S_{21}$  condition. The gate width of an input FET for circuit (b) was chosen to be 200  $\mu\text{m}$  to obtain the input matching. Those for circuits (a) and (c) were 300  $\mu\text{m}$  to lower the noise figure. Each circuit had a 200- $\mu\text{m}$  wide common-source output FET for operation to an external 50- $\Omega$  load. It was found from Fig. 3 that circuit (c) was most suitable for use as a preamplifier among these circuits due to its broad bandwidth and low noise figure.

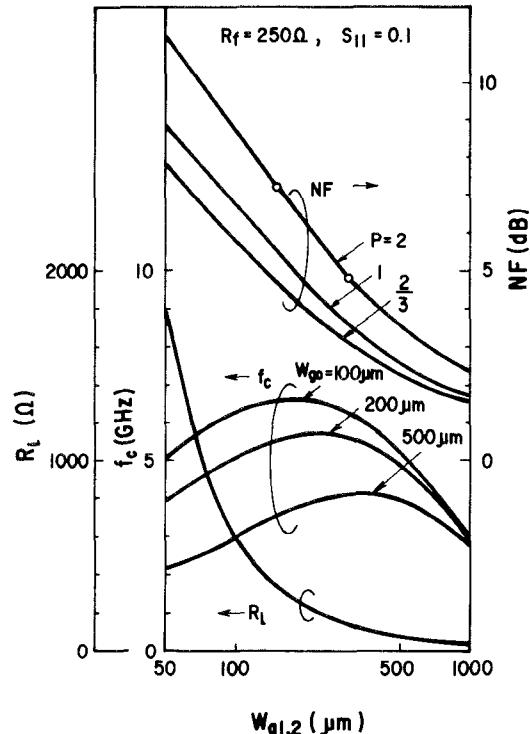

The important design factors to reduce the noise figure for this circuit were the FET gate width and the feedback resistor. Fig. 4 shows  $-3$ -dB bandwidth  $f_c$ , NF, and load resistor  $R_L$  versus the gate widths  $W_{g1,2}$  of the input FET and the source-follower FET with the output FET gate width  $W_{go}$  as a parameter. In this simulation, the feedback resistor was fixed and the load resistor was varied to keep  $S_{21}$  and  $S_{11}$  constant for each output FET gate width. NF was calculated at 1 GHz, assuming that  $P$  was  $2/3$ , 1, or 2, and the small noise contribution of the output FET was not included. Although NF was improved by increasing the gate width, an optimum gate width to obtain the maximum  $f_c$  existed for each  $W_{go}$ . This was because  $f_c$  degraded due to the large input capacitance for large gate width and degraded due to the large load resistor, which was necessary to input matching for a small gate width. For small  $W_{go}$ , large  $f_c$  was obtained and the optimum gate width shifted to a small value because the capacitive load against

Fig. 4.  $-3$ -dB bandwidth  $f_c$ , noise figure NF, and load resistor  $R_L$  versus the gate widths  $W_{g1,2}$  of input FET and source-follower FET with an output FET gate width  $W_{go}$  as a parameter. Transducer gains are 8 dB, 13 dB, and 19 dB for 100- $\mu\text{m}$ , 200- $\mu\text{m}$ , and 500- $\mu\text{m}$  gate-width output FET, respectively. Plotted circles represent experimental results.

the source follower was small. However, the gain to external 50- $\Omega$  load decreased for small  $W_{go}$ .

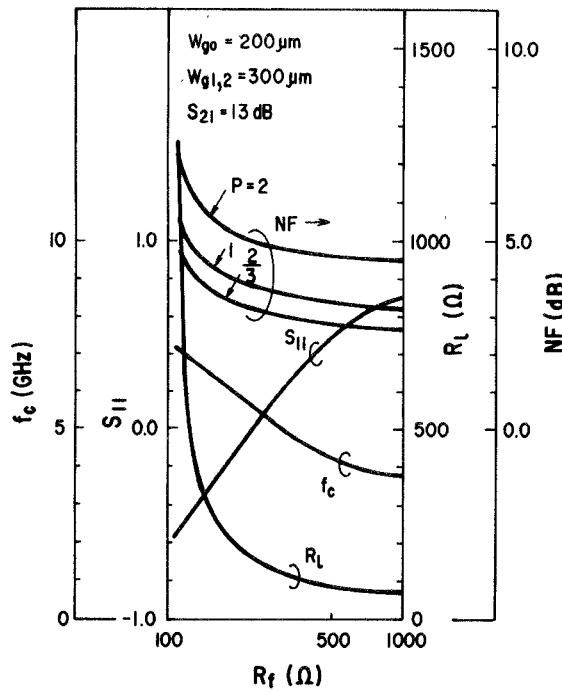

Fig. 5 shows  $f_c$ , NF,  $S_{11}$ , and  $R_L$  versus the feedback resistor  $R_f$  under the constant  $S_{21}$  condition. Gate widths were 300  $\mu\text{m}$  for the input and source-follower FET's and 200  $\mu\text{m}$  for the output FET. The same assumptions given in Fig. 4 were used in the noise calculations. NF improvement in this case was less significant than that seen in Fig. 4. Moreover,  $f_c$  decreased monotonically with increasing feedback resistance due to smaller feedback value, and  $S_{11}$  was changed to keep  $S_{21}$  constant. Therefore, increasing the gate width was more effective for improving the noise figure than increasing the feedback resistor.

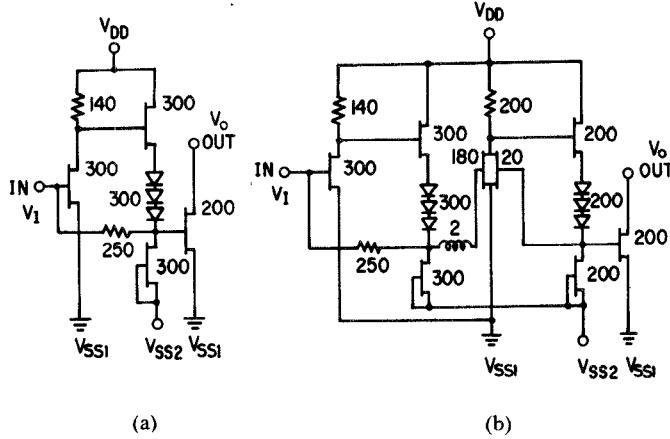

Based on the above results, one-stage and two-stage preamplifiers were designed as shown in Fig. 6. For the one-stage preamplifier, gate widths were designed to be 300  $\mu\text{m}$  for NF below 5 dB as referred to in Fig. 4. For the two-stage preamplifier, a modified circuit with a feedback FET instead of a feedback resistor was cascaded with an interstage inductance to the one-stage preamplifier. The design of the circuit and the interstage inductance is described in the next section. The gate width of the output FET for each amplifier was chosen to be 200  $\mu\text{m}$  for operation to an external 50- $\Omega$  load.  $S_{21}$  and  $S_{11}$  were designed to be 13 dB and 0.1 for the one-stage preamplifier, and 20 dB and 0.1 for the two-stage preamplifier, respectively.

Fig. 5.  $-3\text{-dB}$  bandwidth  $f_c$ , noise figure NF, input reflection coefficient  $S_{11}$ , and load resistor  $R_L$  versus the feedback resistor  $R_f$ .

Fig. 6. Circuits of one-stage and two-stage preamplifiers. Number adjacent to each element represents FET and diode gate widths in microns, resistor values in ohms, and inductance values in nano henries.

### B. The Main Amplifier

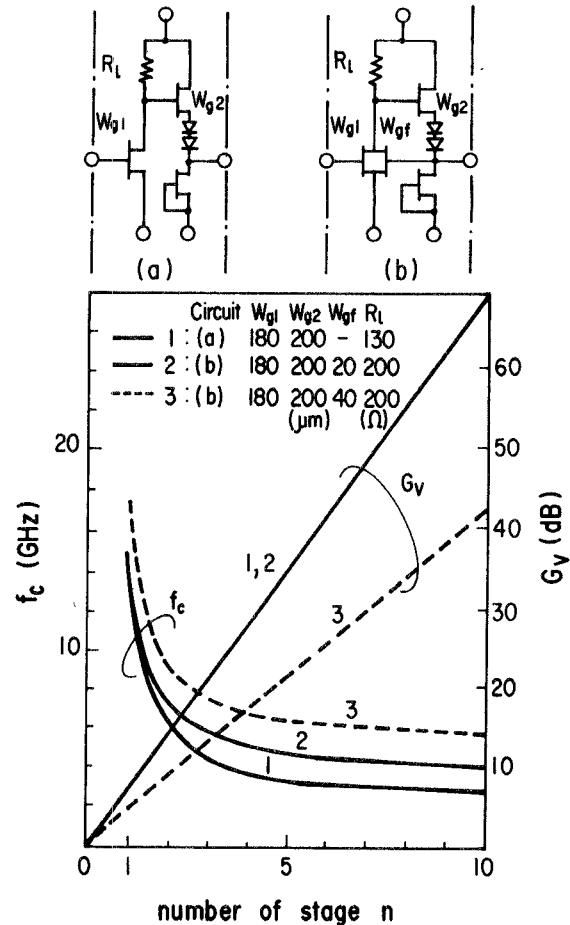

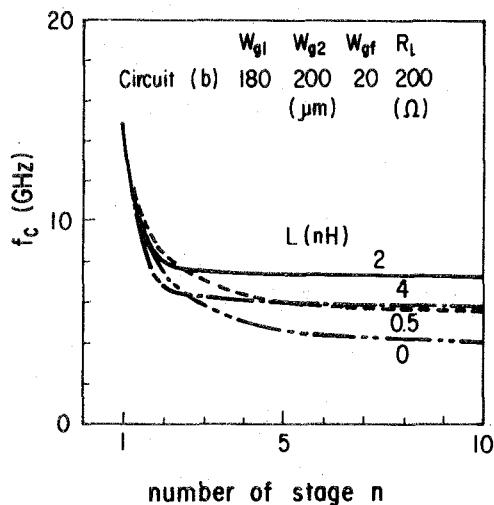

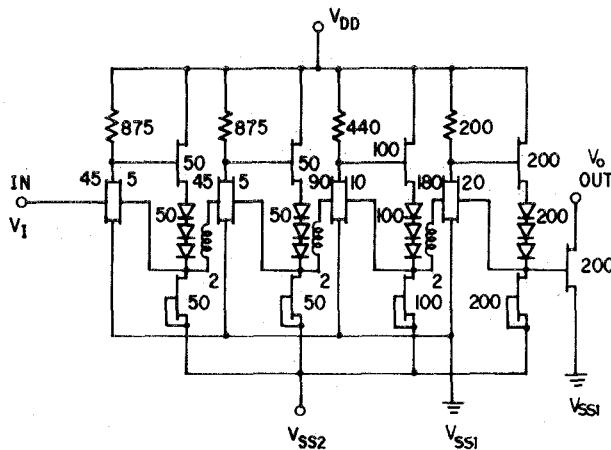

For the main amplifier, it was necessary to optimize a multistage construction to obtain high gain and broad bandwidth. Fig. 7 shows two kinds of direct-coupled circuits and their voltage gain  $G_v$  and  $-3\text{-dB}$  bandwidth  $f_c$  versus the number of amplifier stages. Circuit (a) uses only a common-source FET, and circuit (b) uses a common-source FET with a feedback FET. The gate widths for the input FET and the source-follower FET for each circuit are  $180\ \mu\text{m}$  and  $200\ \mu\text{m}$ , respectively. Circuits (b) with different gate widths for feedback FET's ( $20\ \mu\text{m}$  for case 2 and  $40\ \mu\text{m}$  for case 3) were also compared (Fig. 7). Under the same gain condition, circuit (b) has a larger  $f_c$  than circuit (a). This was because the output impedance of circuit (b)

Fig. 7. Voltage gain  $G_v$  and  $-3\text{-dB}$  bandwidth  $f_c$  versus number of amplifier stages  $n$  with circuits (a) and (b) as unit amplifier stages.

Fig. 8.  $-3\text{-dB}$  bandwidth  $f_c$  versus gate-width ratio  $W_{g2}/W_{g3}$  of a source-follower FET to a next-stage common-source FET.

was reduced by the feedback FET, and bandwidth degradation between the stages became small. Moreover, it was found from Fig. 7 that circuit (b) with the large gate width for the feedback FET had a large  $f_c$  under the same gain condition due to small output impedance. Therefore, circuit (b) was suitable for multistage construction.

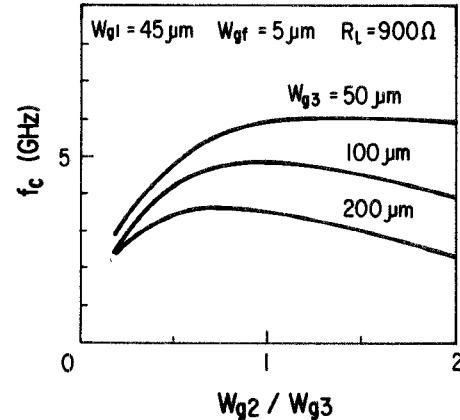

For multistage construction, it was also necessary to optimize the gate width of a source-follower FET to obtain

Fig. 9. —3-dB bandwidth  $f_c$  versus number of amplifier stages  $n$  with an interstage inductance  $L$  as a parameter.

Fig. 10. Circuit of a four-stage main amplifier. Number adjacent to each element represents FET and diode gate widths in microns, resistor values in ohms, and inductance values in nano henries.

the broad bandwidth. Fig. 8 shows  $-3\text{-dB}$  bandwidth  $f_c$  versus the gate-width ratio  $W_{g2}/W_{g3}$  of a source-follower FET to a next-stage common-source FET. In this simulation, gate widths of input and feedback FET's were  $45\text{ }\mu\text{m}$  and  $5\text{ }\mu\text{m}$ , respectively. The ratio of  $W_{g2}/W_{g3}$  had an optimum value for obtaining maximum  $f_c$  for each  $W_{g3}$ . The bandwidth  $f_c$  degraded due to a large source follower input capacitance for large  $W_{g2}/W_{g3}$  and degraded due to a large output impedance for small  $W_{g2}/W_{g3}$ . For small  $W_{g3}$ ,  $f_c$  degradation for large  $W_{g2}/W_{g3}$  was not significant because the capacitive load against the source follower was small.

Bandwidth was also improved by adding an interstage inductance as shown in Fig. 9. In this simulation, circuit (b) of Fig. 7 with a  $180\text{-}\mu\text{m-wide}$  input FET,  $20\text{-}\mu\text{m-wide}$  feedback FET, and  $200\text{-}\mu\text{m-wide}$  source-follower FET was used as a unit amplifier stage and the inductance was varied as a parameter. The interstage inductance has a peaking effect due to a series resonance with the input

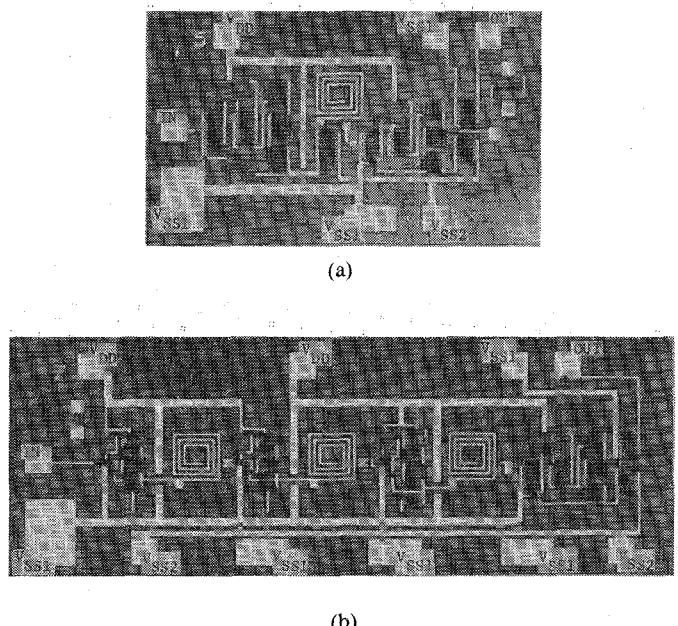

Fig. 11. Microphotographs of the developed GaAs direct-coupled amplifiers. (a) A two-stage preamplifier. (b) A four-stage main amplifier.

capacitance of the next stage. To improve the bandwidth, the inductance should be chosen so that the resonance frequency is located in the neighborhood above the amplifier's  $-3\text{-dB}$  bandwidth without the inductance. In Fig. 9, the optimum value of inductance was  $2\text{ nH}$ . For both smaller and large inductance values,  $f_c$  was degraded because the location of the resonance frequency was not appropriate.

Based on these results, a four-stage main amplifier with interstage inductances was designed as shown in Fig. 10. Total gain was aimed to be  $30\text{ dB}$  with a power consumption of  $670\text{ mW}$ . Gain distribution was designed to be about  $7.2\text{ dB}$  for each stage and about  $1\text{ dB}$  for the output FET. The gate width of an output FET was chosen to be  $200\text{ }\mu\text{m}$  for operation into an external  $50\text{-}\Omega$  load. Gate widths for each stage were chosen to obtain low power consumption as well as broad bandwidth. The gate-width ratio of an input FET to a feedback FET was chosen to be  $9:1$ , i.e.,  $45\text{ }\mu\text{m}:5\text{ }\mu\text{m}$  for the first and second stages,  $90\text{ }\mu\text{m}:10\text{ }\mu\text{m}$  for the third stage, and  $180\text{ }\mu\text{m}:20\text{ }\mu\text{m}$  for the fourth stage. The gate widths of the source-follower FET's were chosen as in Fig. 9, that is, to equal the sum of the source-follower and feedback FET gate widths. Interstage inductances were designed to obtain gain flatness within  $3\text{ dB}$ . Optimization of the inductance value for each stage was not considered in this work and the same value of  $2\text{ nH}$  was used.

#### IV. FABRICATION

The amplifiers were fabricated by self-aligned implantation for  $n^+$ -layer technology (SAINT) [7] and the gate patterns were written directly by E-beam lithography. The details of the fabrication are described in [4] and [10]. The gate length and threshold voltage of the FET were  $0.7\text{ }\mu\text{m}$

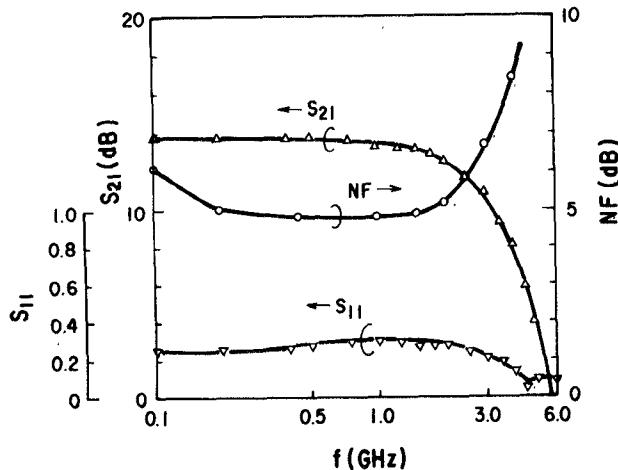

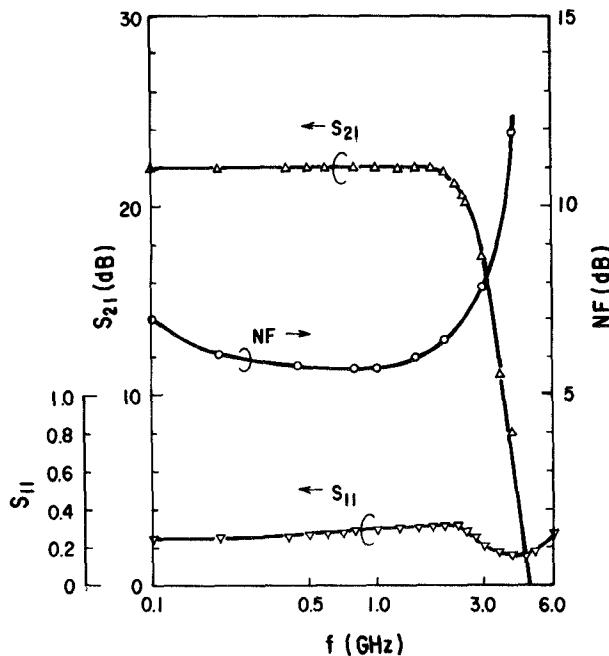

Fig. 12. Frequency dependencies of transducer gain  $S_{21}$ , input reflection coefficient  $S_{11}$ , and noise figure NF for the developed one-stage preamplifier.

Fig. 13. Frequency dependencies of transducer gain  $S_{21}$ , input reflection coefficient  $S_{11}$ , and noise figure NF for the developed two-stage preamplifier.

and  $-1$  V. Fig. 11 shows microphotographs of the two-stage preamplifier and four-stage main amplifier. Chip sizes of the one-stage and two-stage preamplifiers and the main amplifier were  $0.8 \text{ mm} \times 0.8 \text{ mm}$ ,  $0.8 \text{ mm} \times 1.2 \text{ mm}$ , and  $0.8 \text{ mm} \times 2.2 \text{ mm}$ , respectively.

## V. PERFORMANCE

Amplifiers were mounted on a  $50\text{-}\Omega$  coplanar waveguide test fixture and their microwave performance was measured with an automatic network analyzer (HP-8545A) and an automatic noise figure meter (AIL-75).

Frequency dependencies of  $S_{21}$ ,  $S_{11}$ , and NF for the one-stage preamplifier are plotted in Fig. 12. The amplifier was biased at  $V_{DD} = 7$  V,  $V_{ss2} = -4$  V, and  $V_0 = 2$  V. The

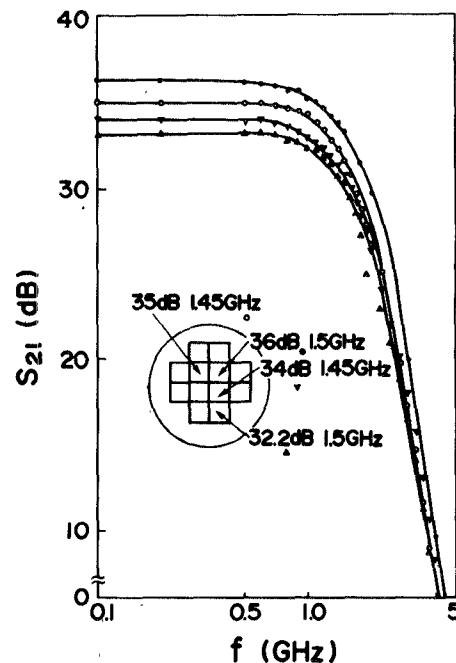

Fig. 14. Frequency dependencies of transducer gain  $S_{21}$  for four main amplifier chips and their locations on the wafer.

TABLE III

PERFORMANCE OF THE DEVELOPED GaAs MONOLITHIC

DIRECT-COUPLED AMPLIFIERS

| Circuit        | Performance |          |         |        |        |

|----------------|-------------|----------|---------|--------|--------|

|                | $S_{21}$    | $S_{11}$ | $f_c$   | NF     | P      |

| Preamplifier   | 14 dB       | 0.26     | 3 GHz   | 4.8 dB | 500 mW |

|                | 22 dB       | 0.25     | 2.7 GHz | 5.6 dB | 960 mW |

| Main amplifier | 36 dB       | —        | 1.5 GHz | —      | 710 mW |

$S_{21}$ : Transducer gain.  $S_{11}$ : Input reflection coefficient.  $f_c$ :  $-3$ -dB bandwidth. NF: Noise figure at 1 GHz. P: Power consumption.

amplifier has a flat gain of 14 dB and  $-3$ -dB bandwidth of 3 GHz with a power consumption of 500 mW.  $S_{11}$  was less than 0.3 over the  $-3$ -dB bandwidth. NF had a minimum value of 4.8 dB around 1 GHz. This noise figure is plotted in Fig. 4, along with measured data from the same amplifier with 150- $\mu\text{m}$  gate-width FET's instead of 300  $\mu\text{m}$ . The measured relationship between NF and gate width agreed well with the calculation for  $P = 2$ . Gain distribution of the amplifier on the wafer was measured at 1 GHz with an RF probe card. All 12 amplifiers on the wafer operated at 1 GHz with uniform performance. Their average gain was 13.2 dB with a standard deviation of 0.45 dB.

Frequency dependencies of  $S_{21}$ ,  $S_{11}$ , and NF for the two-stage preamplifier are plotted in Fig. 13. The amplifier was biased at  $V_{DD} = 8$  V,  $V_{ss2} = -4$  V, and  $V_0 = 2$  V. The amplifier had a flat gain of 22 dB and  $-3$ -dB bandwidth of 2.7 GHz with a power consumption of 960 mW.  $S_{11}$  had nearly the same frequency dependency as that of the one-stage preamplifier. Minimum NF degraded to 5.6 dB compared to the one-stage preamplifier. This was because

the gain of the first stage was not large enough to minimize the noise contribution of the second stage.

Frequency dependencies of  $S_{21}$  for the four main amplifier chips and their locations on the wafer are shown in Fig. 14. Biasing voltages  $V_{DD}$ ,  $V_{ss2}$ , and  $V_0$  were 7 V, -4 V, and 2 V, respectively. The input biasing voltage  $V_I$  was tuned around 0.25 V within the voltage range of  $\pm 0.1$  V. Gain scattering was rather low in spite of the absence of pre-screening steps before microwave measurements. The amplifiers had flat gains of 32–36 dB and -3-dB bandwidth of about 1.5 GHz with a power consumption of 710–790 mW.

Performance of the developed amplifiers is summarized in Table III.

## VI. CONCLUSION

The design and performance of a GaAs direct-coupled preamplifier and main amplifier was described. The developed preamplifiers had 13-dB gain, 3-GHz bandwidth, and 4.8-dB noise figure for a one-stage amplifier, and 22-dB gain, 2.7-GHz bandwidth, and 5.6-dB noise figure for a two-stage amplifier. The developed four-stage main amplifier had 36-dB gain and 1.5-GHz bandwidth with a power consumption of 710 mW. These amplifiers are promising for application to high-speed data communication systems.

## ACKNOWLEDGMENT

The authors wish to thank H. Ito for his useful discussion, the members of the processing group for the fabrication, and M. Hirayama and M. Ohmori for their continuous encouragement.

## REFERENCES

- [1] M. Hirayama, M. Ino, Y. Matsuoka, and M. Suzuki, "A GaAs 4kb SRAM with direct coupled FET logic," in *ISSCC Dig. Tech. Papers*, Feb. 1984, pp. 46–47.

- [2] K. Honjo, T. Sugiura, and H. Itoh, "Ultrabroadband GaAs monolithic amplifier," *Electron. Lett.*, vol. 17, no. 17, pp. 927–928, Nov. 1981.

- [3] D. P. Hornbuckle and R. L. Van Tuyl, "Monolithic GaAs direct-coupled amplifiers," *IEEE Trans. Electron Devices*, vol. ED-28, pp. 175–182, Feb. 1981.

- [4] Y. Imai, H. Ito, K. Ohwada, and T. Sugeta, "Ultra-broad-band GaAs monolithic direct-coupled feedback amplifiers," *IEEE Electron. Device Lett.*, vol. EDL-4, no. 9, pp. 323–325, Sept. 1983.

- [5] D. B. Estreich, "A monolithic wide-band GaAs IC amplifier," *IEEE J. Solid-State Circuits*, vol. SC-17, pp. 1166–1173, Dec. 1982.

- [6] V. Pauker and M. Binet, "Wideband high gain small size monolithic GaAs FET amplifiers," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig. Tech. Papers*, 1983, pp. 71–75.

- [7] K. Yamasaki, K. Asai, T. Mizutani, and K. Kurumada, "Self-align implantation for  $n^+$ -layer technology (SAINT) for high-speed GaAs IC's," *Electron. Lett.*, vol. 18, no. 3, pp. 119–121, Feb. 1982.

- [8] T. Takada, M. Togashi, and T. Hirota, "GaAs MESFET circuit simulation model," *Paper of Tech. Group*, TGSSD83-124, IECE Japan, pp. 9–16, 1983.

- [9] T. Takada, K. Yokoyama, M. Ida, and T. Sudo, "A MESFET variable-capacitance model for GaAs integrated circuit simulation," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 719–724, May 1982.

- [10] N. Kato, K. Yamasaki, K. Asai, and K. Ohwada, "Electron-beam lithography in  $n^+$  self-aligned GaAs MESFET fabrication," *IEEE Trans. Electron Devices*, vol. ED-30, pp. 663–668, June 1983.

**Yuhki Imai** was born in Tokyo, Japan, on March 15, 1955. He received the B.S. degree and the M.S. degree in applied physics from Waseda University.

He joined Musashino Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation, in 1979. He has been engaged in the development of InP and GaAs MESFET's, and the design of monolithic amplifiers. He moved to Atsugi Electrical Communication Laboratory in 1983. He is currently engaged in GaAs MMIC processing.

Mr. Imai is a member of the Institute of Electronics and Communication Engineers of Japan and the Japan Society of Applied Physics.

**Naoki Kato** was born in Aichi Prefecture, Japan, on July 11, 1949. He received the B.S. degree in applied physics from Waseda University and the M.S. degree from Tokyo Metropolitan University.

He joined Musashino Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation, in 1976. He has been engaged in the development of GaAs MESFET's, GaAs digital IC's, and micro-lithography. He moved to Atsugi Electrical Communication Laboratory in 1983. He is currently engaged in GaAs LSI processing.

Mr. Kato is a member of the Institute of Electronics and Communication Engineers of Japan and the Japan Society of Applied Physics.

**Kuniki Ohwada** was born in Sendai, Japan, on October 13, 1944. He received the B.S. degree in physics and the Ph.D. degree in electronic engineering from Tohoku University, Japan, in 1967 and 1984, respectively.

He joined the Electrical Communication Laboratories of Nippon Telegraph and Telephone Public Corporation, Tokyo, in 1967. He is now a Staff Engineer of Atsugi Electrical Communication Laboratory. He has been engaged in research on thin-film capacitors for hybrid integrated circuits, high-speed CMOS devices, CCD transversal filters, buried-channel MOSFET's using a novel isolation technology by oxygen ion-implantation, and very high-speed GaAs memory LSI's. He is presently studying GaAs monolithic microwave integrated circuits.

Dr. Ohwada is a member of the Institute of Electronics and Communication Engineers of Japan and the Japan Society of Applied Physics.

**Takayuki Sugeta** (S'67–M'72) was born in Yamaguchi, Japan, on August 10, 1943. He received the B.S., M.S., and Ph.D. degrees from the University of Tokyo, Tokyo, Japan, in 1967, 1969, and 1972, respectively.

In 1972, he joined the Musashino Electrical Communication Laboratory of Nippon Telegraph and Telephone Public Corporation, where he worked on the R&D of microwave GaAs FET's and high-speed GaAs photodetectors. From 1975 to 1977, he was at the University of Sheffield, Sheffield, England, as a Visiting Research Fellow, where he worked on electrical properties of GaAlAs. Since 1982, he has been engaged in GaAs IC's and ultra-high-speed GaAlAs/GaAs devices for the advanced Information Network Systems (INS). He is now Head of the Compound Semiconductor Device Section of the Atsugi ECL of NTT.

Dr. Sugeta is a member of the Institute of Electronics and Communication Engineers of Japan and the Japan Society of Applied Physics.